目录

- 1、前言

- 2、我这里已有的PAL视频解码方案

- 3、模拟视频概述

- 4、模拟视频颜色空间

- 5、逐行与隔行

- 6、BT656数据与解码

- BT656数据格式

- BT656数据解码

- 7、TW2867芯片解读与配置

- TW2867芯片解读

- TW2867芯片配置

- TW2867时序分析

- 8、设计思路与框架

- 9、vivado工程详解

- Block Design设计

- SDK设计

- 10、上板调试验证并演示

- 11、福利:工程代码的获取

1、前言

大自然的信号都是模拟的,视频信号也不例外。视频信号是指电视信号、静止图象信号和可视电视图像信号。视频信号分为三种制式:PAL、NTSC 和 SECAM。既然 PAL、NTSC、SECAM 都是模拟信号,FPGA 处理的是数字信号(有些 FPGA内部自带 AD,可以处理模拟信号,例如 Altera 的 MAX10),因此中间需要一个芯片做转换,也就是一个 ADC,学名叫做视频解码芯片。

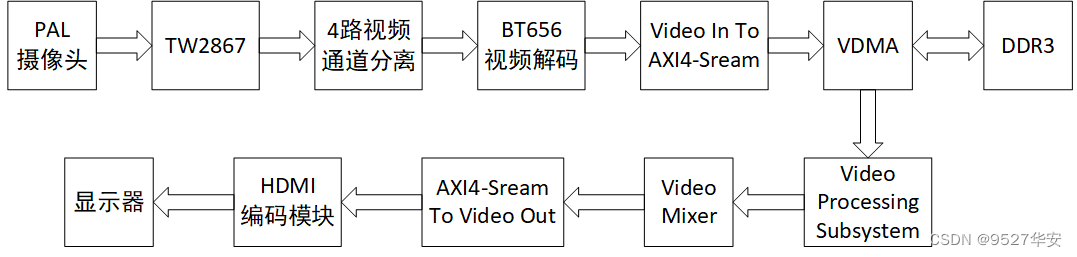

本设计使用TW2867作为视频解码芯片,TW2867可输出PAL或者NTSC,本设计采用PAL制式,TW2867解码出4路BT656视频,然后经过BT656解码,使用VDMA做图像缓存,调用Video Processing Subsystem IP做视频去隔行,再叠加Video Mixer输出1080P背景的视频,最后通过HDMI输出。

本文详细描述了FPGAPAL视频BT656解码Video Processing Subsystem去隔行的设计方案,工程代码编译通过后上板调试验证,文章末尾有演示视频,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

PAL_8">2、我这里已有的PAL视频解码方案

我这里有多种FPGA解码PAL视频的方案,既有PAL解码HDMI输出,也有缩放拼接输出等等,感兴趣的可以去看我的PAL视频解码专栏,专栏地址:https://blog.csdn.net/qq_41667729/category_12336216.html?spm=1001.2014.3001.5482

3、模拟视频概述

大自然的信号都是模拟的,视频信号也不例外。视频信号是指电视信号、静止图象信号和可视电视图像信号。视频信号分为三种制式:PAL、NTSC 和 SECAM,接下来简单介绍一下这对于后期调试电路很有帮助。

PAL 制又称为帕尔制。PAL 是英文 Phase Alteration Line 的缩写,意思是逐行倒相,也属于同时制。“PAL”有时亦被用来指 625 线,每秒 25 格,隔行扫描,PAL 色彩编码的电视制式。NTSC 是 National Television Standards Committee 的缩写,意思是“(美国)国家电视标准委员会”。NTSC 负责开发一套美国标准电视广播传输和接收协议。SECAM 制式,又称塞康制,SECAM 是法文 Sequentiel Couleur A Memoire 缩写,意为“按顺序传送彩色与存储”,是一个首先用在法国模拟彩色电视系统。这只是简单的概述,关于 PAL、NTSC 和 SECAM 更详细的资料请参考视频技术手册。

既然 PAL、NTSC、SECAM 都是模拟信号,FPGA 处理的是数字信号(有些 FPGA内部自带 AD,可以处理模拟信号,例如 Altera 的 MAX10),因此中间需要一个芯片做转换,也就是一个 ADC,学名叫做视频解码芯片,本设计使用TW2867作为视频解码芯片。

4、模拟视频颜色空间

颜色空间也就是颜色的集合。有 3 个最常用的模型:RGB(计算机图形学)、YUV/YCbCr(视频系统)和 CMYK(打印系统)。在此只介绍 RGB 和 YUV/YCbCr。RGB 就是 red、green、blue 的缩写,也就是三原色,常用于计算机图像学中。常用的 RGB 格式有 RGB555、RGB565、RGB888 等。RGB565 含义是 red 占 5bit,green 占6bit,blue 占 5biit,一个占 16bit,颜色深度为 65536 色,常见的存储器有 8bit、16bit等,RGB565 的显示系统非常适合使用这种存储器。

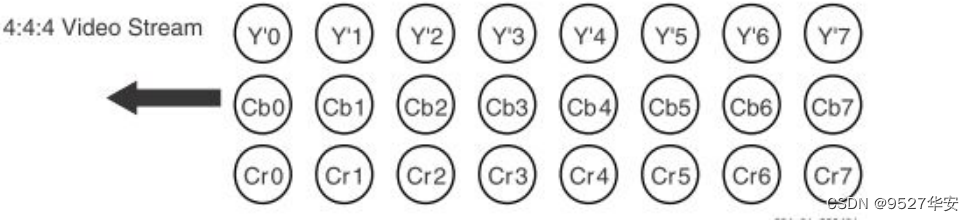

在 YUV/YCbCr 空间中,Y 表示明亮度(Luminance、Luma)信号,U 表示色度(Chrominance)信号,V 表示浓度(Chroma)信号,只是对颜色空间另一种表示方法。常见的 YUV 格式有 YUV422、YUV444 等。YUV444 格式如下图所示,每一个像素分别用24bit 量化,分别量化成 Y、Cb、Cr,各占 8bit,从另一个方面说 YUV444 相当于RGB888,数据量是一样的,YUV444 格式如下图所示:

YUV422 格式如下图所示,它相当于在 YUV444 基础之上丢掉 Cb 和 Cr 数据,2 个像素量化成 32bit 数据,包括 2 个 Y,1 个 Cb,1 个 Cr,相当于 1 个像素需要 16bit 表示,相当于 RGB565 数据量。

TW2867输出的是YUV422 格式。

5、逐行与隔行

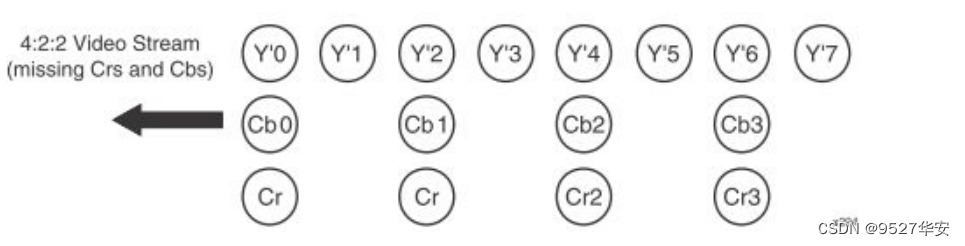

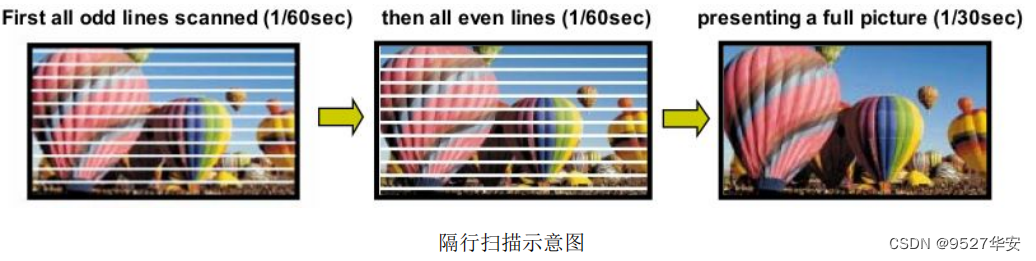

先简单区分一个概念,隔行扫描(Interlace scan)和逐行扫描(Progressive scan)。如下图所示,这是隔行扫描示意图,也就是先显示奇数行,然后再显示偶数行,这只是其中一种隔行扫描的方式,用途比较广泛,除此之外还有隔 2 行、隔 3 行扫描。

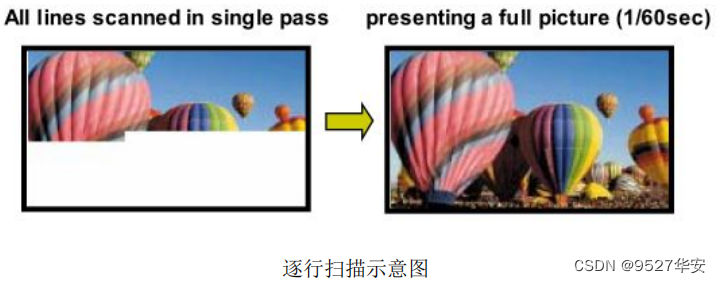

如下图所示,这是逐行扫描示意图,也就从第一行扫描,一直扫描到最后一行。目前显示器是逐行扫描的。

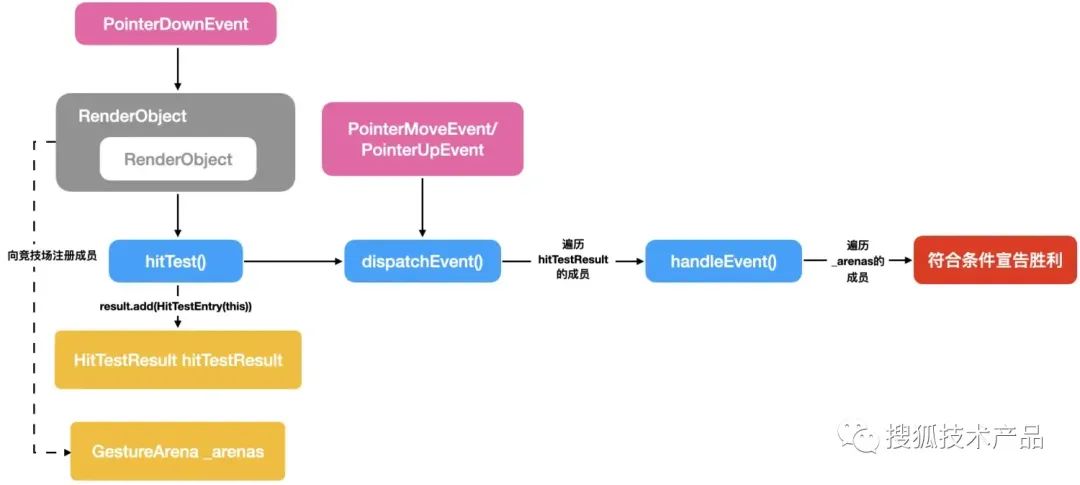

6、BT656数据与解码

BT656数据格式

BT656 是一种视频输出格式,TW2867 视频输出是 BT656 格式,只有一小部分不一样,BT656 格式时钟是 27MHz,输出视频格式是 YUV422,隔行输出。

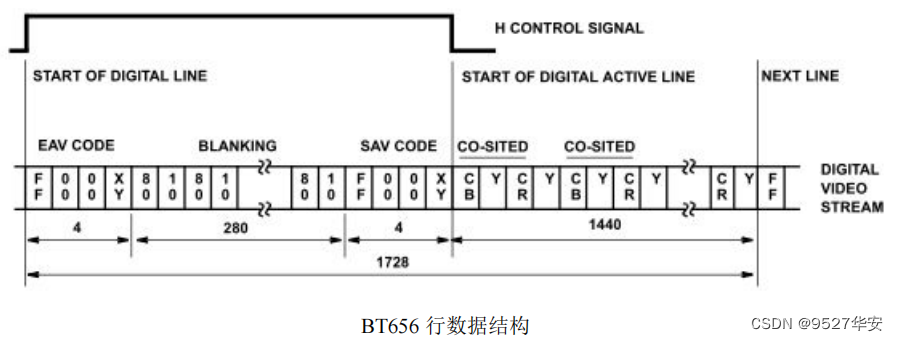

如上图所示是一行 BT656 数据结构,分成 4 段:EAV(4-byte)、BLANKING(280-byte)、SAV(4-byte)和有效数据(1440-byte),接下来分别介绍。BLANKING:280-byte,0x80 和 0x10 交替出现。有效数据:1440-byte,一共 720 个像素,Y 占 720 个数据,Cb 和 Cr 分别占 360 个数据。EAV 和 SAV:分别占 4-byte,前三个字节相同,是 0XFF,0X00,0X00,最后一个不同,根据这个字节进行解码。

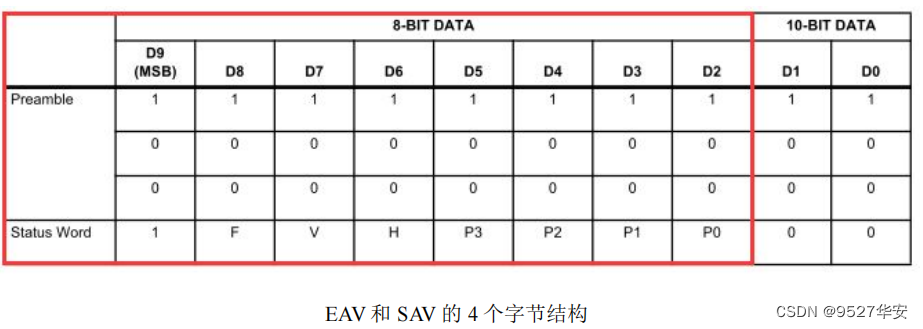

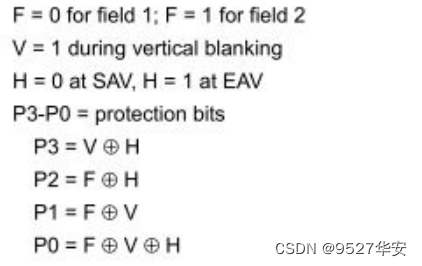

EAV 和 SAV 的结构如上图所示,其中 F、V、H 含义:

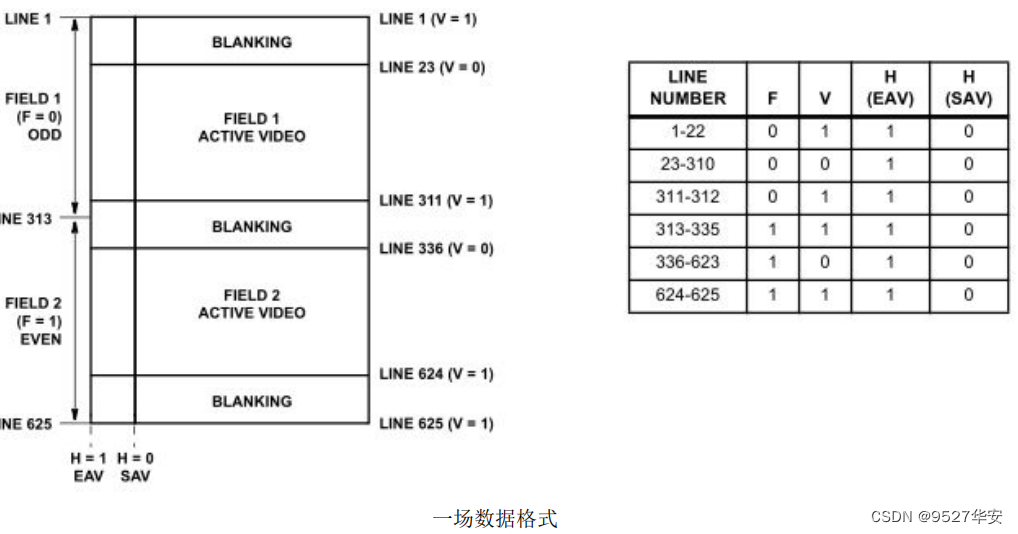

F 是场信号,0 表示场 1,1 表示场 2,也就是奇偶场。V 表示场有效,0 表示场数据有效,1 表示是垂直消隐。H 区分 EAV 和 SAV 信号。P3-P0 只是校验保护位,由 F、V、H 进行异或运算得到。如下图所示,这是一帧 BT656 数据格式,一共包括 625 行,每行 1728 个字节,有效数据大小是 720x576,分成 2 场,每场 720x288,其余行是消隐信号。

BT656 规定一行有 1728 个字节,一帧有 625 行,每秒传输 25 帧数据,8bit 总线并行传输。1728x625x25=27000000=27M,经过计算就知道 27MHz 的来历了。在这 625行中有用的数据是 576 行,在 BT656 视频格式中有效视频大小是 720x576,其余的当做消隐处理。

BT656数据解码

压力来了,怎样才能做好 BT656 解码来适应不同的模块呢?根据BT656数据格式,解析并丢弃EAV(4-byte)、BLANKING(280-byte)、SAV(4-byte),保留有效数据(1440-byte),同时恢复行同步、场同步、奇偶场号、数据有效以及像素数据,详细内容请参考工程代码。

7、TW2867芯片解读与配置

TW2867芯片解读

本次设计使用的是专用模拟视频解码芯片 TW2867,支持 4 路模拟视频输入,4 路模拟音频输入,1 路音频输出,视频输出是标准 BT656 格式。由于 FPGA 引脚限制,MIS603 音频部分没有做;TW2867输入 4 路模拟视频信号,输出YUV422数字视频流,每路视频流是 BT656 格式,BT656 视频时钟 27MHz,4 路复合 =27MHzx4=108MHz,视频接口连接到 FPGA。

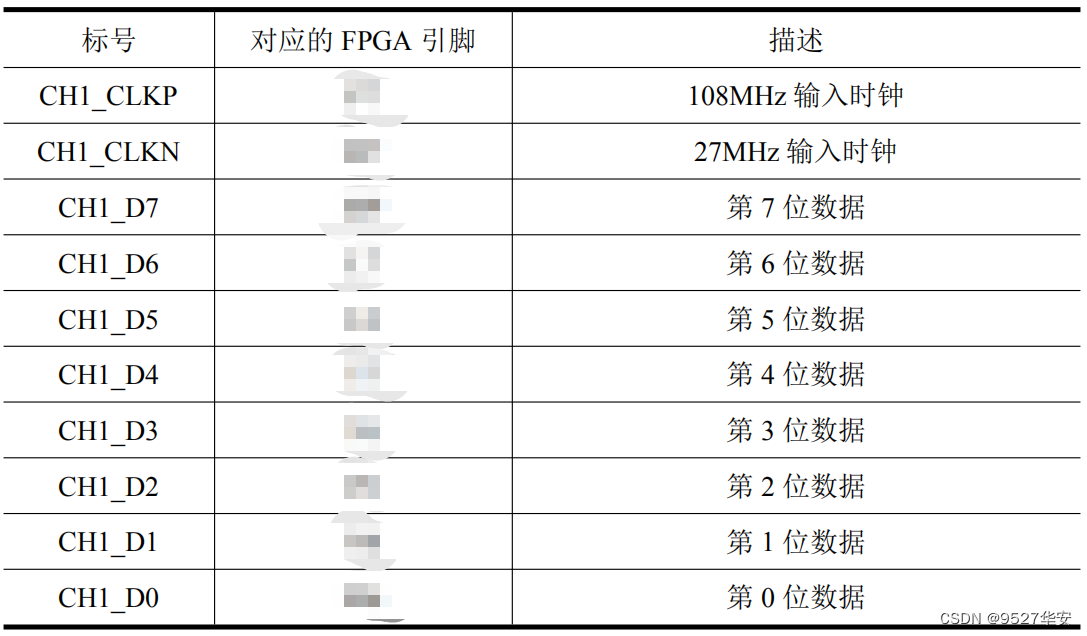

TW2867视频输出引脚说明如下:

对于 4 路复合视频时钟 108MHz,对硬件要求很高,数据线和时钟线等长布线。

TW2867芯片配置

TW2867 内部有很多寄存器,在此给出几个常用的寄存器及其含义,更多的内容请参考 TW2867 数据手册。

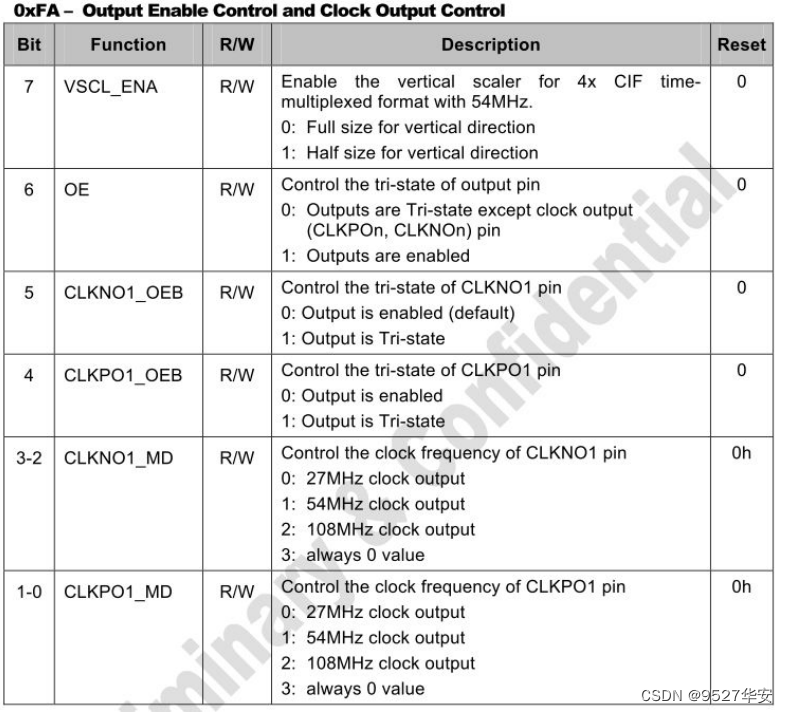

输出使能控制和时钟输出控制:

在这个寄存器中主要关心bit6配置为1,输出使能;bit3-2配置为0,CLKNO1输出27MHz时钟,bit1-0 配置为 2,CLKPO1 输出108MHz 时钟,通过这 2 个时钟可以把 4 路视频信号分开。这个寄存器配置为 0x42。

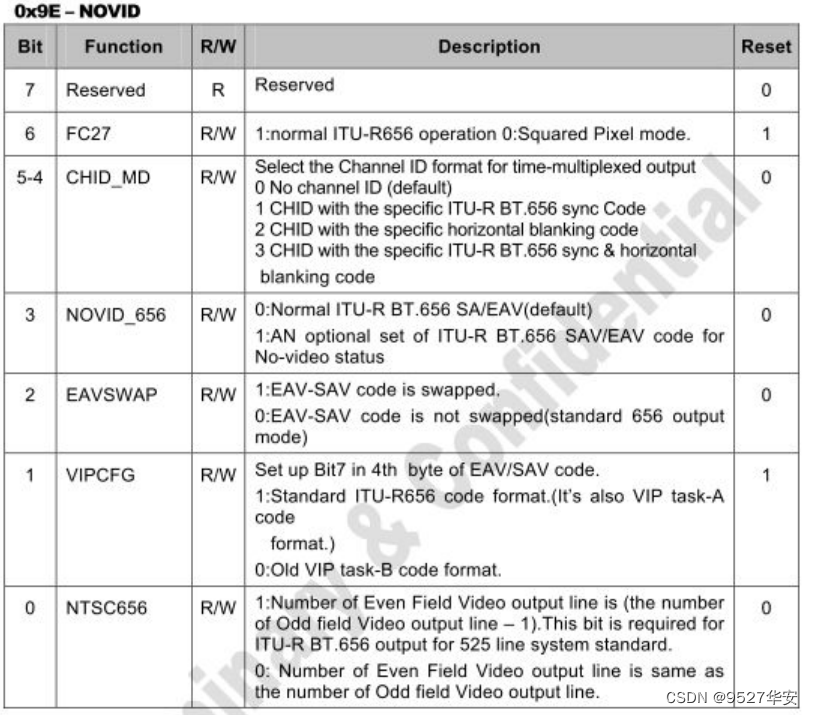

Bit6:配置为 1,标准 ITU-R656 格式。

Bit5-4:选择视频复合后输出引脚,配置为 1,从 CHID1 输出。

Bit3:配置为 0,正常 ITU-R656 格式。

Bit2:配置为 0,输出视频中有 EAV-SAV 信号。

Bit1:配置为 1,bit7-4 是 EAV/SAV 编码。

Bit0:配置为 0,奇数场和偶数场行数相等。

综上,这个寄存器配置为 0x52。

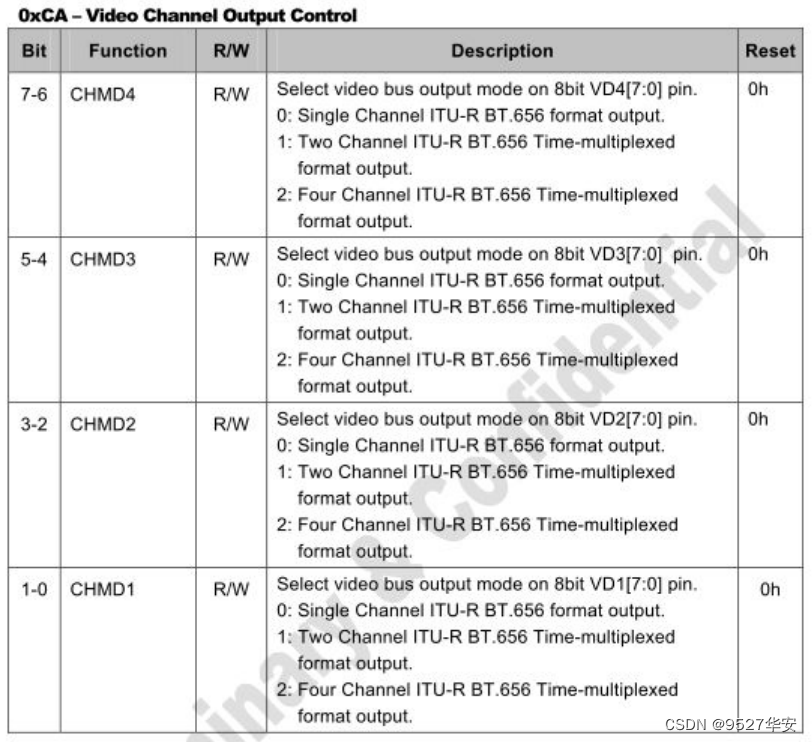

视频通道输出控制:

这个寄存器配置为 0x02,4 路视频通过时分复用到 VD1[7:0]输出,硬件设计连接到 VD1。

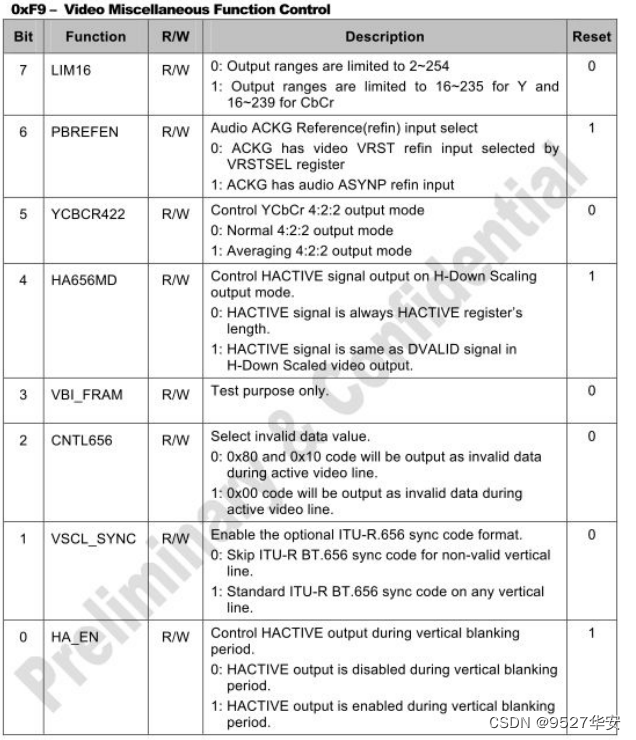

视频功能控制:

Bit7:配置为 0,视频视频数据输出限制到 0-254。

Bit6:配置为 1,ACKG 的输入参考是 ASYNP。

Bit5:配置为 0,输出格式是 YUV422 格式。

Bit4:配置为 1。

Bit3:配置为 0,仅用于测试。

Bit2:配置为 0,消隐时数据输出 0x80 和 0x10。

Bit1:配置为 0,ITU-R BT656 同步信号在消隐部分。

Bit0:配置为 1,HACTIVE 在垂直消隐期间使能。

这个寄存器配置为 0x51。

TW2867时序分析

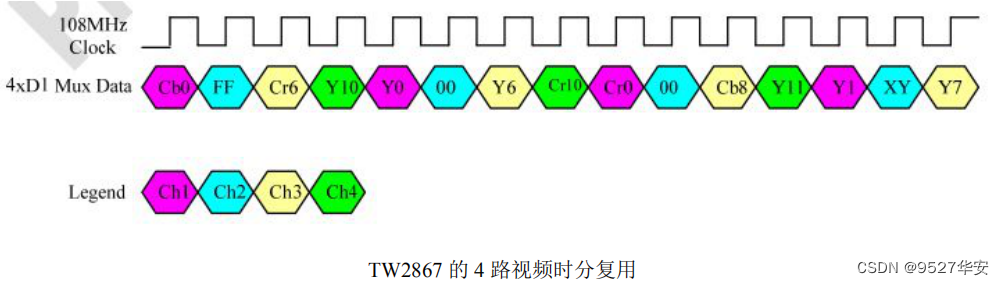

之前介绍了 BT656 格式时钟 27MHz 的来源,TW2867 支持 4 路实时 BT656 视频,采样时分复用,最大时钟频率是 108MHz,因此需要一个 108MHz 的时钟输入引脚,考虑到方便解调出每路视频信号增加了一个 27MHz 的时钟输入信号,再加上 8 根数据,这样 10 根线就可以输入 4 路视频信号,在硬件设计上大大简化,降低了布线的复杂度。

如下图所示,TW2867 在 4 路视频复合时的时序图,那就是 4 个通道视频轮流输出,即通道 1 视频数据、通道 2 视频数据、通道 3 视频数据、通道 4 视频数据,然后重复。

通过了解视频数据复合方式,那解复合程序就可以设计了,那面说说思路。采用时分复用,每个通道数据轮流输出,那就需要一个计数器实现把每个通道的数据分离,即将 108MHz 时钟数据分成 4 个 27MHz 时钟数据。由于是 4 路视频,需要产生一个模长为 4 的计数器,根据计数器的数据把数据分配到 4 个视频通道上。详细内容请参考工程代码。

8、设计思路与框架

设计思路与框架如下:

图像输入:

1路PAL摄像头,TW2867解码为yuv422视频,TW2867支持4路输入,这里仅输入一路;

4路视频通道分离:

将4路复合视频分离出4路独立的视频通路,这里只有1路,所以输出的4路视频只有1路有效;

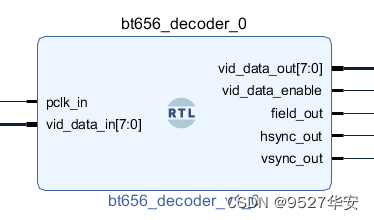

BT656解码:

BT656解码模块接口如下图:

解码BT656,恢复出行、场、de、数据,BT656解码模块输出的是YUV422视频;

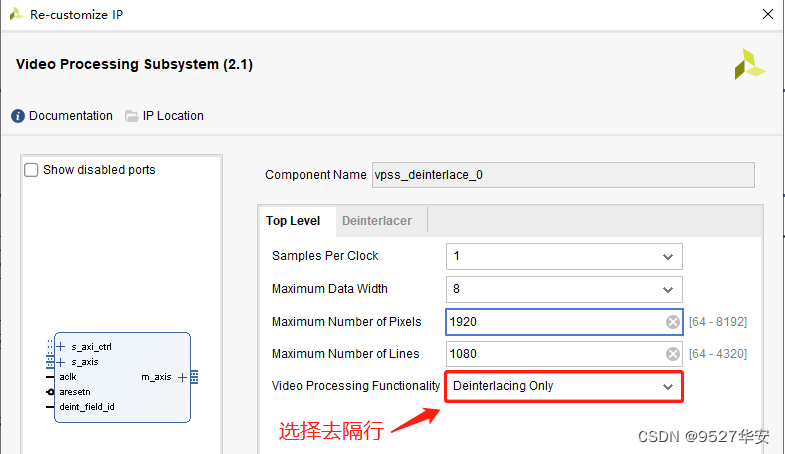

Video Processing Subsystem去隔行:

调用Xilinx官方Video Processing Subsystem IP去隔行,IP配置如下:

图像缓存:

调用Xilinx官方的以VDMA为核心的一堆IP做图像缓存,这是Xilinx图像缓存的经典套路,但因为输入的是PAL视频,所以这些IP的配置还是很有讲究的,具体打开工程看吧;

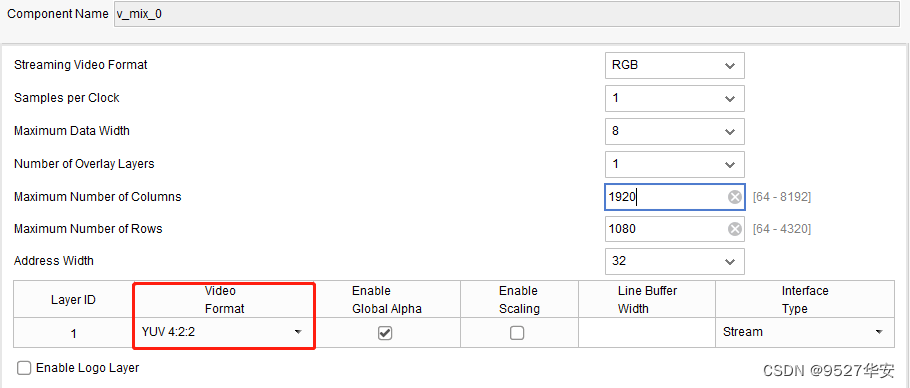

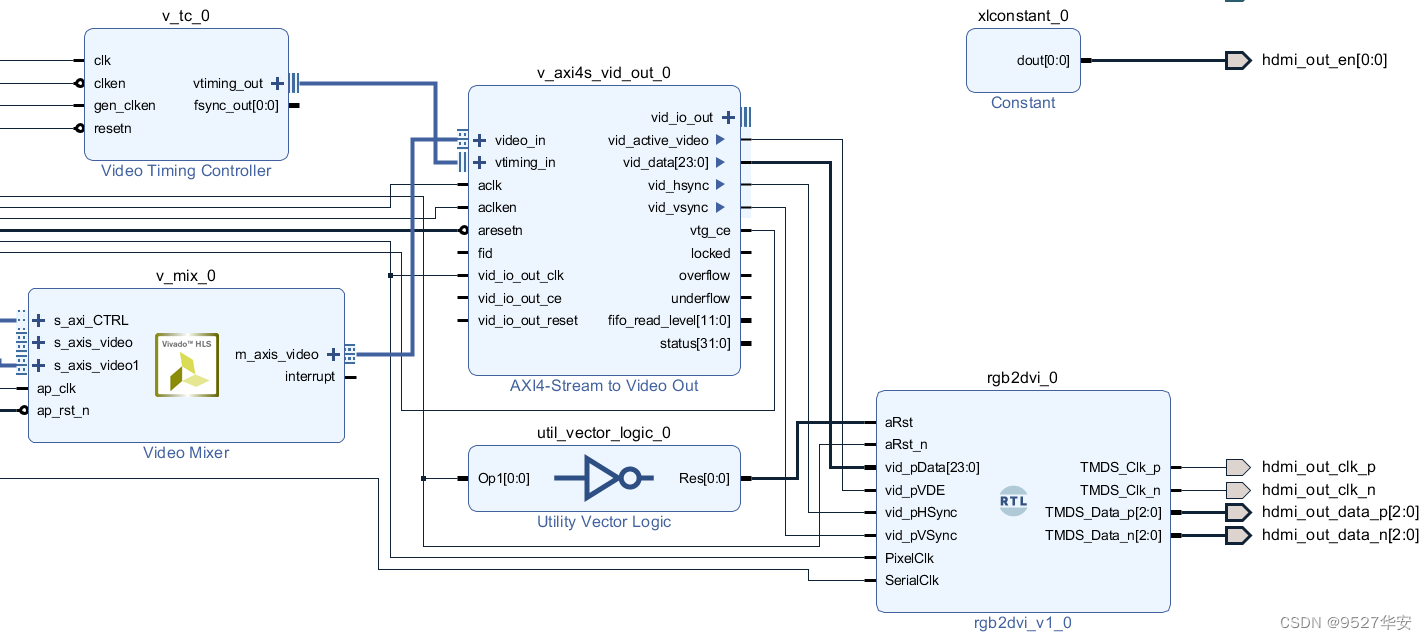

图像输出:

因为PAL视频的分辨率是720x576,所以调用一个Video Mixer做图像叠加,背景设置为1920x1080,叠加720x576的视频输出,输出HDMI视频,很简单,不多说。Video Mixer配置如下:

9、vivado工程详解

开发板:Xilinx–Xilinx-xc7k325tffg676-2;

开发环境:vivado2019.1;

输入:1路PAL摄像头;

输出:HDMI,1920x1080;

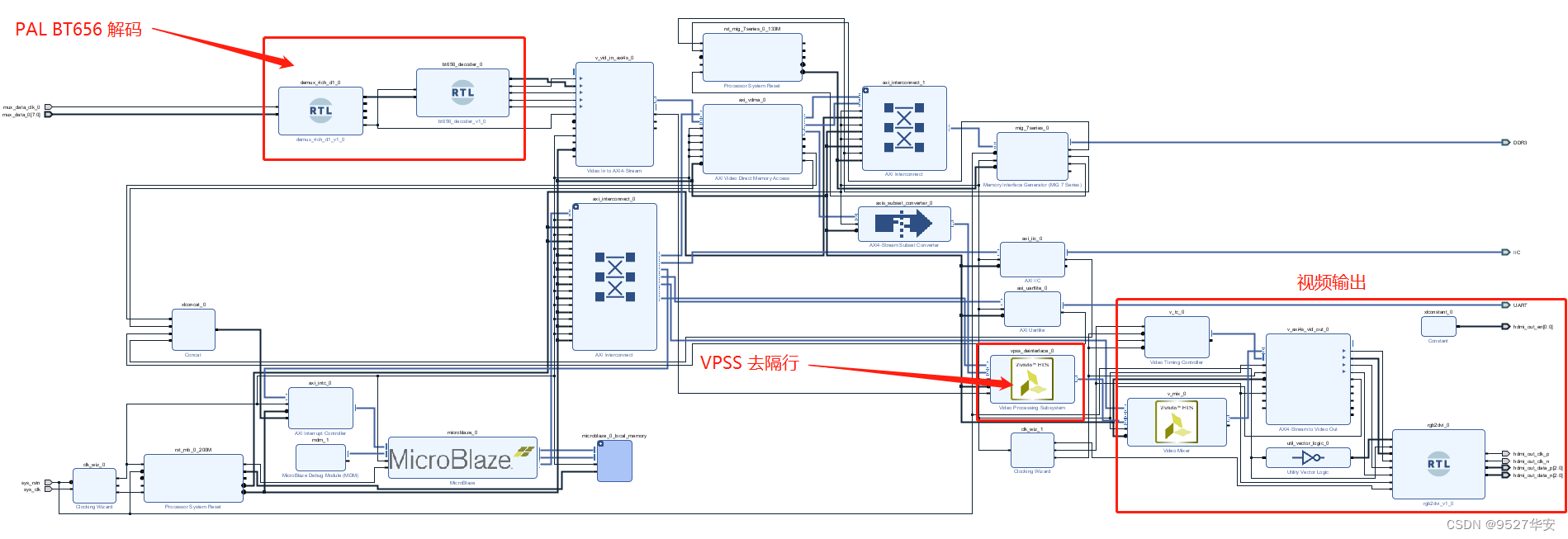

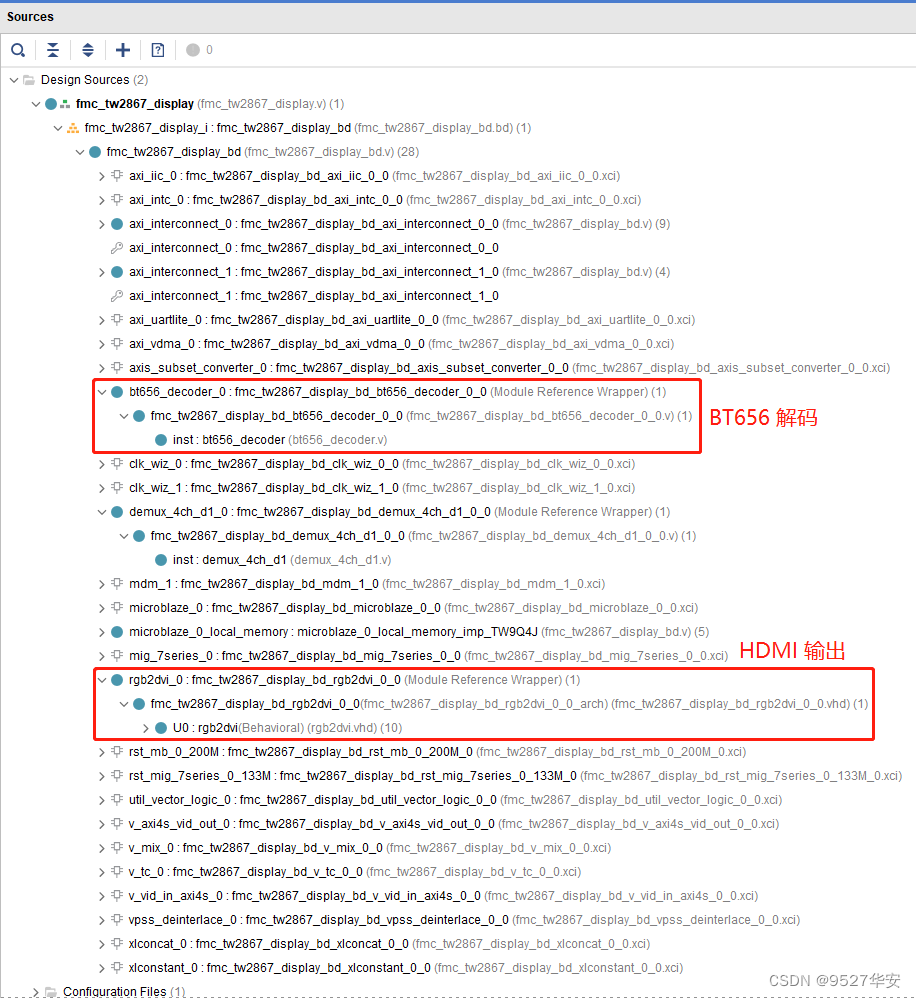

Block Design设计

工程Block Design如下:

综合后的工程代码架构如下:

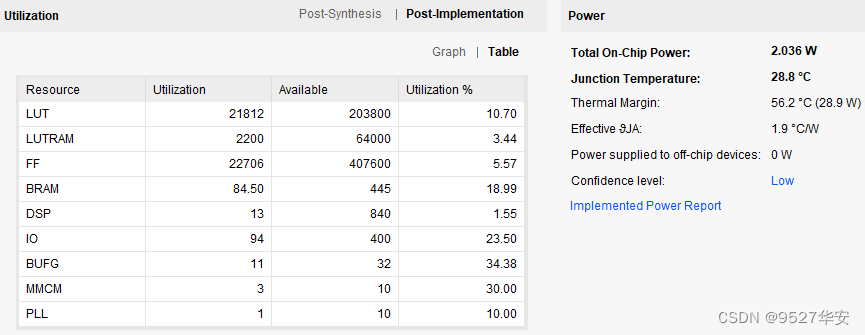

综合编译后的FPGA资源消耗和功耗预估如下:

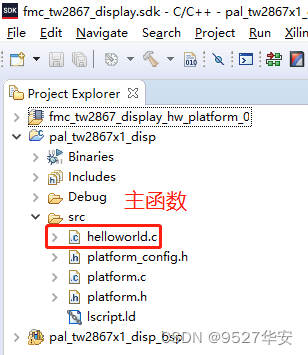

SDK设计

SDK代码架构如下:

SDK主函数如下:

int main(void) {

/* Initialize tw2867, set to PAL (720x576) mode */

xil_printf("\n\rInitialize tw2867, set to PAL (720x576) mode.\n\r");

tw2867_init(PAL_VIDEO_TYPE);

/* Initialize VDMA device */

xil_printf("\n\rInitialize VDMA device.\n\r");

vdma_init(AXIVDMA_0_BASEADDR, DDR_BASEADDR + 0x01000000);

/* Initialize VPSS device */

xil_printf("\n\rInitialize VPSS device.\n\r");

vpss_init(XVPROCSS_0_BASEADDR);

/* Initialize Mixer device */

xil_printf("\n\rInitialize Mixer device.\n\r");

mixer_init();

xil_printf("\n\rConfiguration completed, please check the output image!\n\r");

while(1);

return XST_SUCCESS;

}

SDK实现的功能主要如下:

1:初始化 TW2867,设置为 PAL(720x576)制式;

2:初始化 VDMA,将 1 路视频数据缓存至 DDR;

3:初始化 VPSS,将图像去交错;

4:初始化 Mixer,将 1 路视频进行叠加;

10、上板调试验证并演示

由于某些保密因素,暂无法展示实物,请见谅。。。

输出如下:

11、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: