left join

php

操作系统

图像阴影消除

C6678

GPT-3

Lock

Documents PDF

select函数

433MHz自发电无线控制器

知识产权

研究报告

sqlite3

外观模式

onenet

Owner

手持技术

商城推荐系统

大学课程设计

Python安装

VHDL

2024/4/12 0:39:07作业2:用Verilog语言实现二十进制计数器

1.新建一个工程,并且加入一个Verilog-HDL文件,参考例程中的代码编写Verilog语言,编写完成后如下图所示

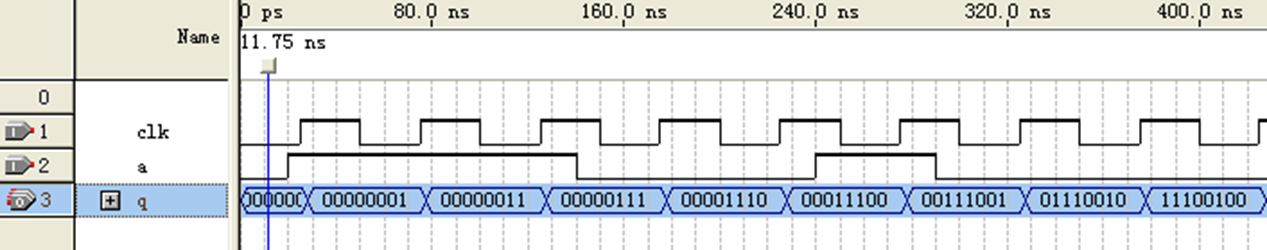

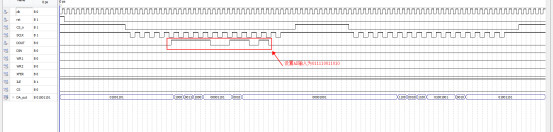

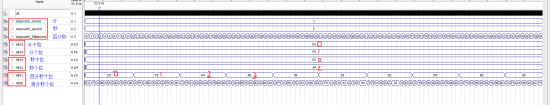

编译后,查看RTL文件如下图所示 建立VWF文件,添加仿真信号后观察仿真结果如下图

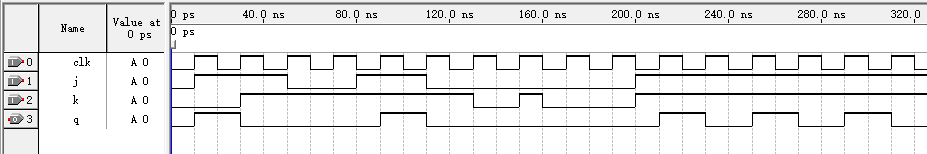

作业2:用Verilog实现12进制计数器

1.新建工程文件

2.新建Verilog文件,注意文件名称必须与工程相同, 编写完成后的文件如下图所示

通过TOOL工具栏的相关选项查看工程的RTL文件如下图所示 通过建立VWF仿真文件,并且加入使能信号、时钟信号后观察仿真的结果如下图所示。

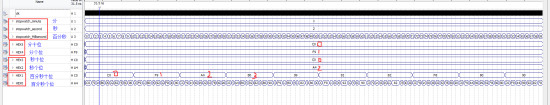

FPGA-VHDL实现10进制减法计数器——基于ISE14.7平台

本文使用VHDL语言设计10进制减法计数器,附带清零和置数功能。将项目分为分频器、计数器、数码管三个部分,采用元器件例化的方式,自顶向下设计。 目录一、代码1.1 顶层文件1.2 分频器1.3 计数器1.4 数码管二、仿真一、代码

1.1 顶层文件 顶层…

VHDL: found ‘0‘ definitions of operator “+“, cannot determine exact overloaded...问题解决

目录一、问题二、解决一、问题 使用Xilinx ISE14.7编写VHDL代码时,出现以下问题:

found 0 definitions of operator "",

cannot determine exact overloaded matching definition for ""翻译过来就是:找到运算符“”的“0”定义&a…

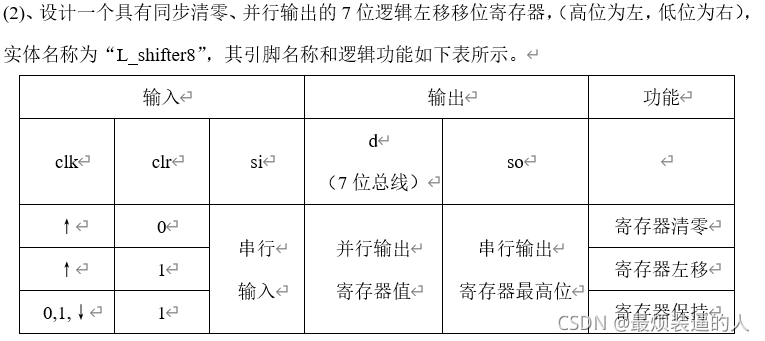

FPGA入门实验五:多周期移位寄存器

题目要求 1.根据题目要求新建Verilog创建对应的module并生成 symbol,代码如下 移位寄存器 / module shift_reg_SIPO( RST , // 异步复位, 高有效 CLK , // 时钟,上升沿有效 EN , // 输入数据串行移位使能 IN , // 输入串行数…

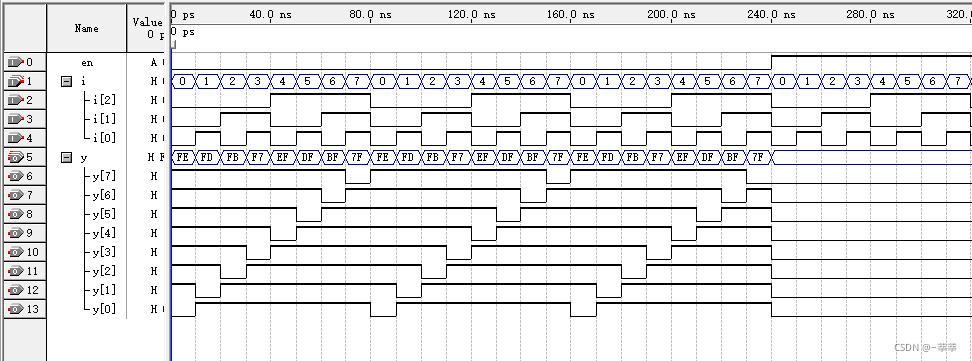

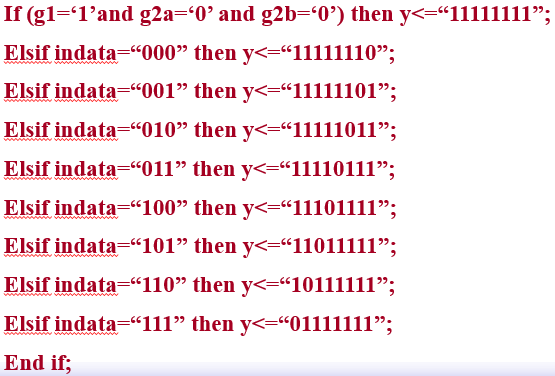

《VHDL数字系统设计与应用》在校课程记录——实验四:组合逻辑3-8译码器的设计实验

一、概述: 二、VHDL 描述:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY decoder_38 ISPORT(i : IN STD_LOGIC_VECTOR(2 DOWNTO 0);en : IN STD_LOGIC;y : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END decoder_38;ARCHITECTURE one OF decoder_38 I…

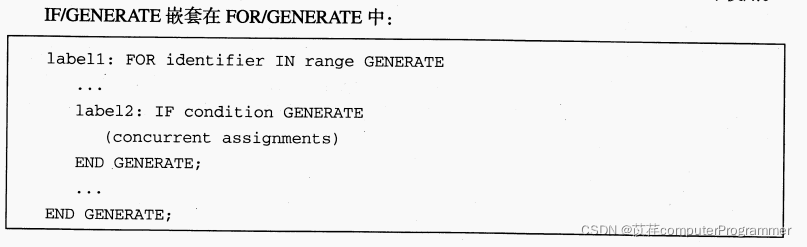

硬件描述语言VHDL之并行语句基本使用介绍

硬件描述语言VHDL之并行语句1. process语句1.1 基本介绍1.2 基本格式1.3 代码示例2. 简单形式并行信号赋值语句2.1 简单并行信号赋值语句说明2.2 代码示例3. 条件信号赋值语句3.1 基本格式3.2 代码示例4. 选择信号赋值语句4.1 基本格式4.2 代码示例5. block块语句5.1 简单说明5…

使用VHDL语言控制相机

将CMOS相机与ZYNQ-7000系列FPGA SoC连接,并将实时视频输入输出到VGA屏幕。

硬件

软件

概述

在这个项目中,我们将从头开始构建一个FPGA映像平台。 目的是将VGA分辨率CMOS相机与MiniZed Development板连接,并将获取的实时视频输入输出到VGA…

VHDL语言基础-组合逻辑电路-概述

目录 概述:

组合逻辑电路:——电路无记忆功能

组合逻辑电路的设计方法:

传统的设计方法:采用标准组件进行设计

组合逻辑电路的设计方法:

两种设计方法的比较: 概述:

数字电路按其完成逻辑…

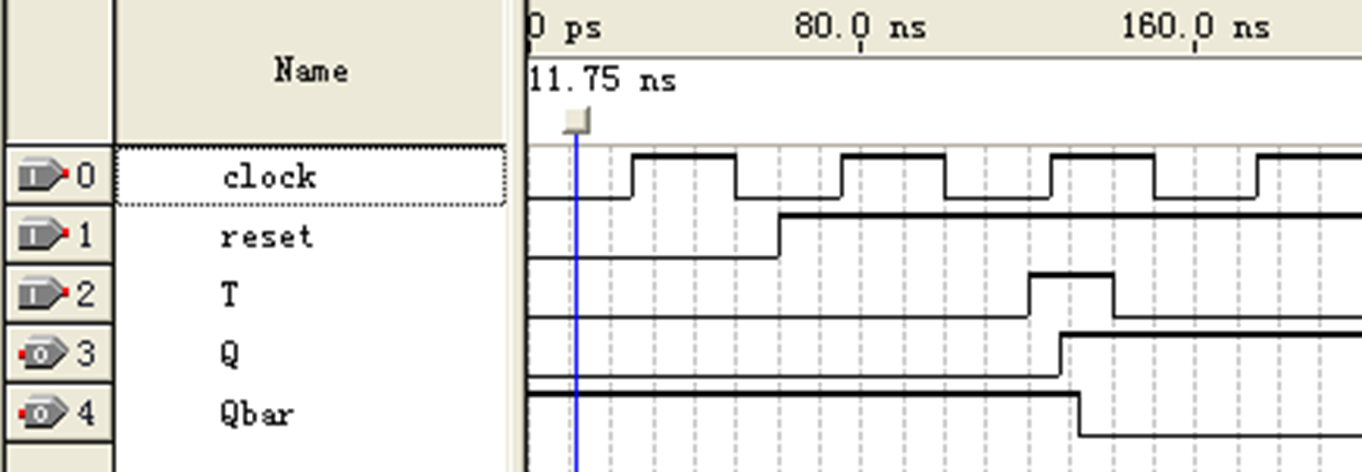

VHDL语言基础-时序逻辑电路-触发器

目录 触发器:

D触发器:

触发器的VHDL描述:

触发器的仿真波形如下:编辑

时钟边沿检测的三种方法:

方法一:

方法二:

方法三:

带有Q非的D触发器:

带有Q非的D触发器的描述&am…

《VHDL数字系统设计与应用》在校课程记录——实验五:触发器设计实验

一、D 触发器:

1、概述: 2、VHDL 描述:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;entity DFF1 isport (clk,d : in std_logic;q : out std_logic);

end entity;architecture rtl of DFF1 is

beginp1:…

硬件描述语言VHDL之顺序语句基本使用介绍

硬件描述语言VHDL之顺序语句1. 顺序赋值语句1.1 变量赋值语句1.1.1 基本说明1.1.2 使用举例1.2 信号赋值语句1.2.1 简单说明1.2.2 使用举例1.3 常量赋值语句1.3.1 简单说明1.3.2 使用举例2. wait语句2.1 简单说明2.2 基本形式2.3 代码示例3. if语句3.1 基本格式3.2 二选一if语句…

《VHDL数字系统设计与应用》在校课程记录——实验七:计数器设计实验

一、实验内容:

1、设计一个 5 进制减法计数器,并将结果显示在数码管上。

2、设计一个有时钟使能的 2 位十进制计数器,有拨码开关,可以控制加法或减法,并将结果显示在数码管上。 二、实验步骤:

数码管显示…

《VHDL数字系统设计与应用》在校课程记录——实验六:七段数码显示设计实验

一、模块准备:

创建工程时将老师给的显示模块和分频模块的 .vhd 文件加入到工程中:

1、显示模块的 VHDL 模型:

--//**-----------------文件信息-----------------------------------

--//**文 件 名: decl7s.vhd

--//**创 建 人…

《VHDL数字系统设计与应用》在校课程记录——实验三:基本组合逻辑电路的 VHDL 模型

一、新建工程 二、新建 VHDL 文件:

1、新建 VHDL File: 2、保存文件

注意:文件名必须和实体名一样

三、编写程序:

1、可以插入 VHDL 程序模板: 或者右击选择Insert Template打开: 2、编写程序ÿ…

74161设计二十进制计数器

1. 2^4<20<2^8,因此在设计中要用到两片74161芯片。

2. 新建BDF文件,保存工程。

3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示 图1. 二十进制计数器连接图

4.建立VWF文件,仿真后得到结果如图2 图2、 仿真结…

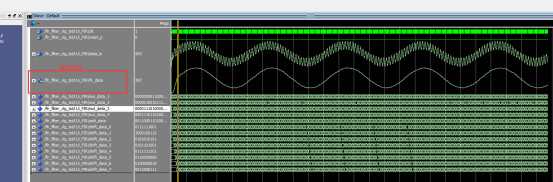

FPGA入门实验六:计数器、ROM和DDS

1.新建工程并添加Verilog和BDF文件,Bdf文件如下图: 2.RTL图如下: 3.用signal tap 对Out信号在Bus Line 模式下观察: 回答问题: 1)电路的工作频率是50Mhz,正弦波频率和计数器增量值的对应关系是什么 答&…

FPGA入门实验一: 项目创建、编译和下载

1.选择New Project Wizard 新建一个工程,工程名称和顶层文件名称相同,如下图

2.选择芯片型号 Cyclone III 下484个引脚的EP3C16F484C,然后直接点击Finish完成创建即可。 3.为工程添加.BDF文件,取名和工程文件相同 4.在BDF文件的空…

Zynq UltraScale+ XCZU5EV 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计…

Zynq7020 纯VHDL解码 MIPI 视频,HDMI输出,支持 ISP 动态配置,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图OV5640摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块RGB转HDMI模块ISP 动态配置OV5640输入分辨率控制OV5640调焦控制OV5640输入数据格…

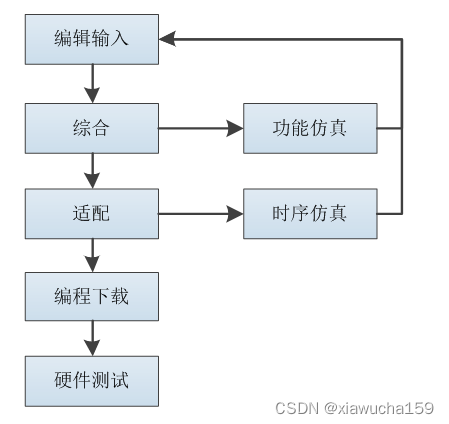

5.什么是EDA技术

目录什么是EDA技术?概念分析EDA的设计流程什么是EDA技术?

概念

EDA(ELEctrinic design automation)是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理和智能化技术等,进行电子产品自动化设计的一门新技术。 使用…

FPGA解码4line MIPI视频 IMX291/IMX290摄像头采集 提供工程源码和技术支持

目录1、前言2、Xilinx官方主推的MIPI解码方案3、我已有的MIPI解码方案4、纯Vhdl代码解码MIPI5、vivado工程介绍6、上板调试验证7、福利:工程代码的获取1、前言

FPGA图像采集领域目前协议最复杂、技术难度最高的应该就是MIPI协议了,MIPI解码难度之高&…

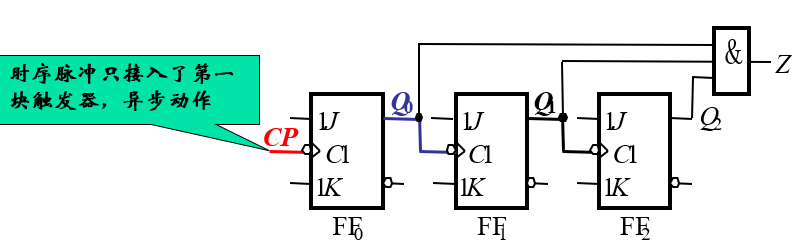

VHDL语言基础-时序逻辑电路-概述

目录 时序逻辑电路-概述:

时序逻辑电路:

时序逻辑电路——有记忆功能:

时序电路的分类:

按照触发器的动作特点:

按照输出信号的特点:

同步时序逻辑电路:

异步时序逻辑电路: 时序逻辑电路-概述:

数字电路按其完成逻辑功能的不同特点,划分为组合逻辑电路和时序…

VHDL基础知识笔记(2)

1.赋值语句: (1)在VHDL中,只能在VHDL程序的并行部分进行信号说明,但是可以在VHDL的并行语句和顺序语句中同时使用信号的赋值语句。 (2)变量的说明和赋值语句只能在VHDL程序的顺序语句部分进行说…

VHDL中数组赋值写法

VHDL中数组赋值写法VHDL中不允许对数组直接赋值 ,先对变量赋值,再由变量赋值给数组才可以。参考代码中对iram_128_t_mem(i) 赋值写法。library IEEE;

use IEEE.std_logic_1164.all;entity iram_128_t isport (WE : in std_logic;CLK : in std_logic;ADDR…

音乐播放器VHDL蜂鸣器数码管显示简谱,视频/代码

名称:音乐播放器数码管显示简谱蜂鸣器

软件:Quartus

语言:VHDL

代码功能:

设计音乐播放器,播放一首歌,使用开发板的蜂鸣器播放音乐,使用Quartus内的ROM IP核存储音乐文件,使用数…

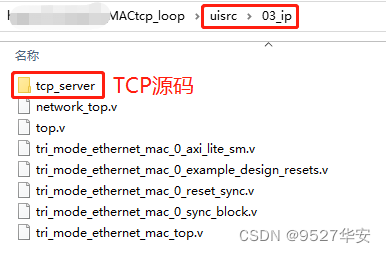

FPGA实现 TCP/IP 协议栈 纯VHDL代码编写 提供数据回环工程源码和技术支持

目录 1、前言2、我这里已有的以太网方案3、该TCP/IP协议栈性能4、详细设计方案TCP/IP协议栈MAC数据通路TCP数据回环 5、vivado工程1-->B50610 工程6、vivado工程2-->RTL8211 工程7、vivado工程3-->88E1518 工程8、上板调试验证并演示准备工作ping测试TCP数据回环测试 …

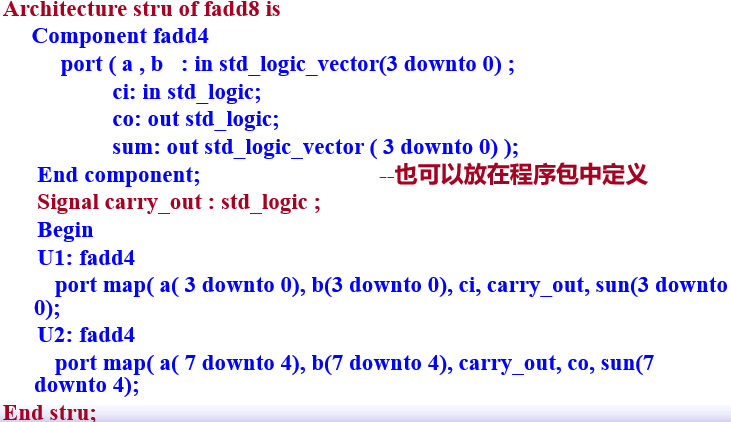

VHDL语言基础-组合逻辑电路-加法器

目录 加法器的设计:

半加器:

全加器:

加法器的模块化:

四位串行进位全加器的设计:

四位并行进位全加器:

串行进位与并行进位加法器性能比较:

8位加法器的实现: 加法器的设计&…

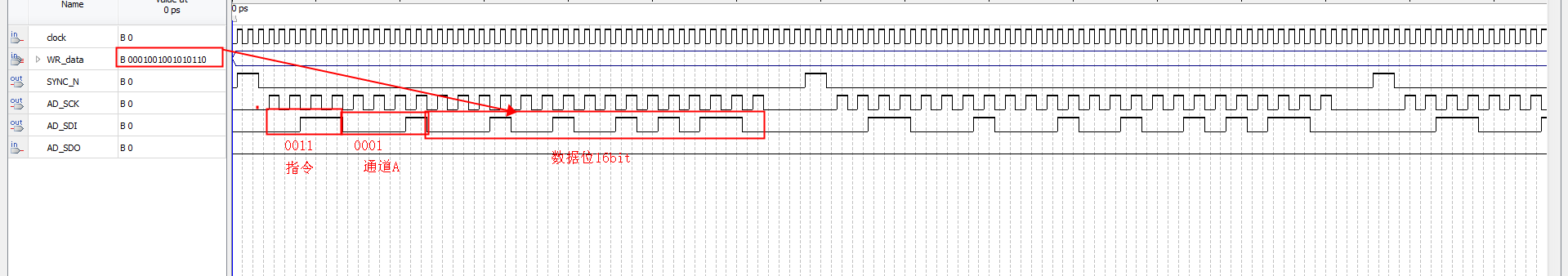

AD7321代码SPI接口模数转换连接DAC0832输出verilog

名称:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出

软件:QuartusII

语言:VHDL

代码功能:

使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后…

Zynq UltraScale+ XCZU15EG 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计…

FPGA设计FIR滤波器低通滤波器,代码及视频

名称:FIR滤波器低通滤波器

软件:Quartus

语言:Verilog/VHDL

本资源含有verilog及VHDL两种语言设计的工程,每个工程均可实现以下FIR滤波器的功能。 代码功能:

设计一个8阶FIR滤波器(低通滤波器ÿ…

用74161设计十二进制计数器

1.74161为十六进制计数器,设计十二进制计数器时1片就可以满足要求。

2.新建BDF文件及保存工程同前篇。

3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示 图1 十二进制计数器连接图

4.建立VWF文件,仿真后得到结果如图2

FPGA入门实验二:译码器组合逻辑

题目(1):放置2个2-4译码器模块,则总共有2组SW,每组2个,2组LED,每组4个,每组SW分别控制其对应的LED组

1.新建VHDL-Verilog文件,并写一个2-4译码器的moudle,并…

使用 FPGA 评估板学习 VHDL

特点

使用 Arrow 经济实惠且适合面包板的 FPGA 开发板 (BeMicro MAX 10) ,创建光传感器、温度传感器、运动传感器和汽车显示器学习 FPGA 和电子学背后的理论,包括理解正在发生的事情所需的数学和逻辑了解什么是 FPGA 以及它与微控制器或 ASIC 的区别设置…

VHDL语言基础-组合逻辑电路-译码器

目录 译码器的设计:

译码器的分类:

常用译码器:

3-8译码器:

3-8译码器的描述:

小结: 译码器的设计:

译码器和编码器是数字系统中广泛使用的多输入多输出组合逻辑部件。

实现译码的组合逻…

密码锁设计(不完整)-VHDL

小白萌新,思路仅供参考,问题较多,有待改善 设计要求 4个按键为密码输入键,可以用另一个按键作为复位,当按下复位按键时可以重新开始输入新的密码。利用一位数码管显示输入密码的次数,另一位显示正确与否&am…

FPGA(VHDL)控制伺服

这一次,我们将看看如何控制一个普通的 RC 爱好舵机。它们有许多不同的尺寸和传动装置,但对于基本控制,它们都使用简单的 PWM(脉宽调制)信号来指示所需的位置。

脉冲宽度应在 1000 到 2000s 之间,其中 1500…

FPGA的音乐彩灯VHDL流水灯LED花样,源码和视频

名称:FPGA的音乐彩灯VHDL流水灯LED

软件:Quartus

语言:VHDL

代码功能:

(1)设计一彩灯控制电路,按要求控制8路(彩灯由发光 二极管代替,受实验箱限制,多路同…

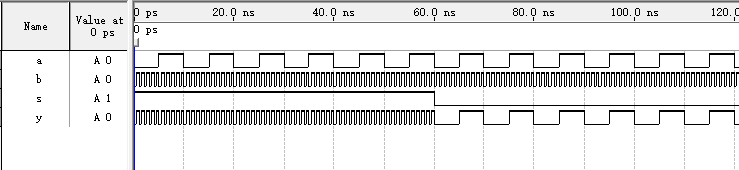

编码器、译码器、数据选择器的实现 (VHDL语言) [数字逻辑与数字系统实验一]

VHDL语言实现编码器译码器数据选择器1. 编码器1.1 实验要求1.2 逻辑符号1.3 实现代码1.4 仿真测试2. 译码器2.1 实验要求2.2 逻辑符号2.3 实现代码2.4 仿真测试3. 数据选择器3.1 实验要求3.2 逻辑符号3.3 实现代码3.4 仿真测试1. 编码器 1.1 实验要求

设计4-16译码器

具有使能…

调查报告——FPGA 与图像处理

数字图像处理是指将图像信号转换成数字信号并对其进行处理的过程。数字图像处理在当代社会发展中发挥着不可替代的作用,它广泛应用于几乎所有与成像有关的领域,如航空航天、生物医学工程、工业检测、机器人视觉、公安司法、军事制导、文化艺术等。随着低…

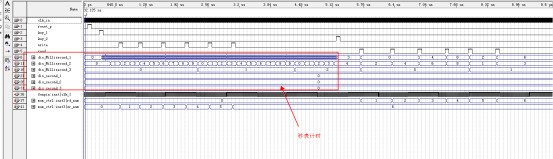

FPGA入门实验三:计数器、波形仿真、SignalTap

题目(1):参照代码,设计一个0-17的计数器,当计数值为17的时候,OV输出1,其他输出0,注意设定合理的信号位宽。

1.新建工程,添加BDF文件和Verilog-HDL文件,写一个…

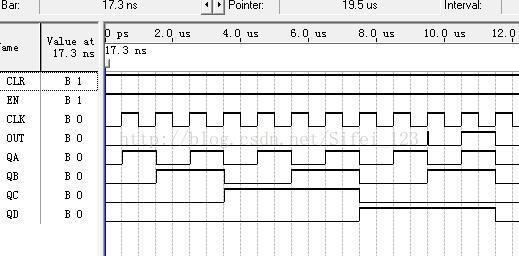

FPGA入门实验四:时间基准电路 和 带使能的多周期计数器

题目要求:

1.根据参考代码,将计数器范围改为0~15,verilog 代码如下:

module CNT_EN( input wire CLK, input wire EN, output reg [4-1:0] OUT, output reg OV ); always (posedge CLK) begin if(EN1&&OUT<15) O…

作业2:4-16进制译码器Verilog 语句实现

1.根据工程向导新建一个工程。

2.新建VHDL-Verilog 文件,注意文件名称必须和工程名称相同。编写完成的Verilog文件如下图

3.将工程进行编译,看是否报错,无误后可以进行下一步操作。

4.查看RTL文件如下图所示 5.建立仿真VWF文件,…

作业2:循环计数器Verilog实现

1.根据工程向导新建工程

2.新建一个Verilog-HDL文件,编写相关的Verilog语句,如下图所示 3.在TOOL下的选项中查看RTL图,如下图所示。 4.建立VWF文件,添加输入信号,然后观察仿真结果如下图所示

VHDL语言基础-时序逻辑电路-寄存器

目录 寄存器的设计:

多位寄存器:

多位寄存器的VHDL描述:

移位寄存器:

串进并出的移位寄存器的VHDL描述: 寄存器的设计:

多位寄存器:

一个D触发器就是一位寄存器,如果需要多位寄存器&…

FPGA简易加减法计算器设计

题目要求: (1)设计10以内的加减法计算器。 (2)1个按键用于指定加法或减法,一个用于指定加数或被加数,还有两个分别控制加数或被加数的增加或减少。 (3)设置的结果和计算的…

FPGA(VHDL)语音识别

在Altera DE0上使用MATLAB和VHDL的简单语音识别系统。

介绍

该项目是一个试验,目的是在低端和教育性FPGA(如Altera DE0)上开发简单的语音识别引擎。 耗尽低端FPGA的局限性并驯服它们来做高级工作也是一个简单的挑战。

设计该系统的目的是识…

20210123 张大佳MCU VHDL常用语法 ---- Port map and OPEN

VHDL常用语法 ---- Port map and OPEN

FPGA---基本功 日常记录 备忘

Two ways to map the PORTS of a COMPONENT during its instantiation:

1 第一种 变量和引脚关联方式 Positional mapping, ports x and y correspond to a and b, respectively.

COMPONENT inverter …

数字秒表设计仿真VHDL跑表,源码,视频

名称:简单秒表设计仿真VHDL跑表

软件:Quartus

语言:VHDL

代码功能:

数字秒表功能描述

本次练习只需要一个数码管(假设该数码管已被选中),实现数码管显示功能,具体要求如下(设数码管为共阳)

1)实现秒表计时功能。…

超详细-Vivado配置Sublime+Sublime实现VHDL语法实时检查

目录

一、前言

二、准备工作

三、Vivado配置Sublime

3.1 Vivado配置Sublime

3.2 环境变量添加

3.3 环境变量验证

3.4 Vivado设置

3.5 配置验证

3.6 解决Vivado配置失败问题

四、Sublime配置

4.1 Sublime安装Package Control

4.2 Sublime安装VHDL插件

4.3 语法检查…

FPGA分频电路设计(2)

实验要求: 采用 4 个开关以二进制形式设定分频系数(0-10),实现对已知信号的分频。

类似实验我之前做过一次,但那次的方法实在是太笨了: 利用VHDL实现一定系数范围内的信号分频电路 需要重做以便将来应对更…

verilog常用系统任务和函数

在FPGA开发中编写仿真测试激励文件(testbench),经常会用到verilog的系统函数,使用系统函数非常方便,本文总结了常用的系统函数,并提供了说明和使用示例。一、文件操作1、打开文件$fopen和关闭文件$fclosein…

FPGA的256点FFT调用Quartus IP核实现VHDL傅里叶变换

名称:256点FFT调用Quartus IP核实现傅里叶变换

软件:Quartus

语言:VHDL

代码功能:使用VHDL实现256点FFT,调用Quartus IP核实现傅里叶变换

演示视频:http://www.hdlcode.com/index.php?mhome&cView…

FPGA开发软件(vivado + modelsim)环境搭建(附详细步骤)

本文详细介绍了vivado软件和modelsim软件的安装,以及vivado中配置modelsim仿真设置,每一步都加文字说明和图片。一、软件安装包下载1、vivado vivado版本很多,目前最新的已更新到vivado2022.2,版本越高,安装包越大&…

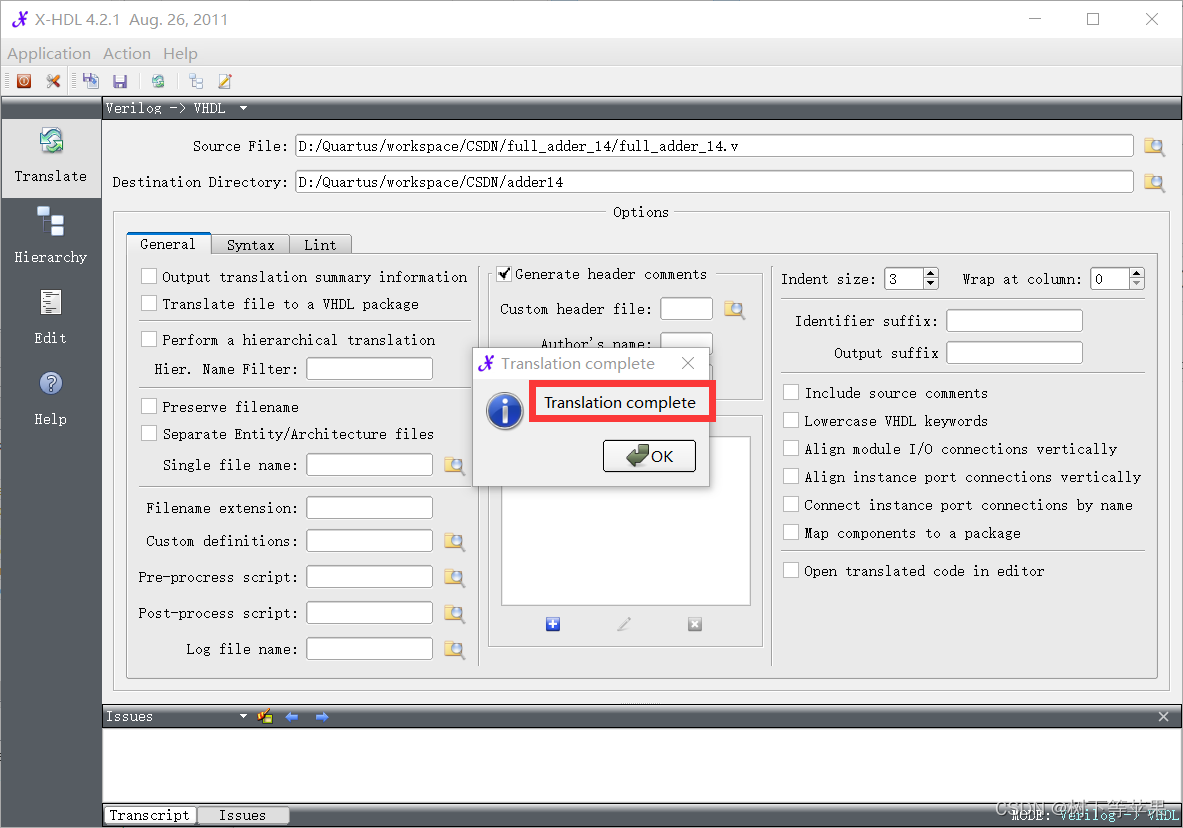

Verilog与VHDL代码转换工具X-HDL的安装、使用教程(详细)以及报错:Translation error的解决办法

一、安装 1、获取安装包: 链接:https://pan.baidu.com/s/12CuBeF2NNCnjLpAn6hpL6A 提取码:zwfz 2、解压压缩包,运行X-HDL-4.2.1-Setup.exe。 (1)弹出以下对话框,根据使用语言选择(没…

Zynq UltraScale+ XCZU9EG 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计…

Verilog与VHDL的一些比较

1.列表

verilogVHDLincludeLIBRARY IEEEmoduleENTITYarchitecturealwaysprocesswire/regsignalassign<阻塞-组合逻辑<非阻塞-时序逻辑posedge clk(negedge)clk’event and clk ‘1’

2.图例 图例来源网络,有空可以敲一遍

Quartus II 13.0第一次使用和仿真(VHDL)

Quartus II仿真软件使用1. 创建文件2. 创建项目3. 编译一下4. 仿真创建5. 添加引脚6. 设置时间7. 编译运行8. 小BUG当前使用VHDL语言进行代码编写 1. 创建文件 代码编写:(一位加法器) Ctrls保存文件 注意文件名和实体一致起来 2. 创建项目 Next->Next->…-&g…

DAC芯片AD5689控制代码SPI接口FPGA代码,视频

名称:DAC芯片AD5689控制代码SPI接口

软件:QuartusII

语言:VHDL

代码功能: 控制DAC芯片AD5689,通过芯片的SPI接口,进行命令和地址、数据写入,控制DAC输出模拟信号。 AD5689/AD5687采用多功能S…

数字秒表VHDL启动暂停清零,源码和视频

名称:数字秒表VHDL启动暂停清零(代码在文末付费下载)

软件:Quartus

语言:VHDL

代码功能:

数字秒表

使用VHDL语言设置数字秒表。要求具有百分秒、秒和分钟显示,百分秒范围00-99,秒范围00-59,分钟范围0…

数字秒表VHDL实验箱精度毫秒可回看,视频/代码

名称:数字秒表VHDL精度毫秒可回看

软件:Quartus

语言:VHDL

代码功能: 数字秒表的VHDL设计,可以显示秒和毫秒。可以启动、停止、复位。要求可以存储6组时间,可以回看存储的时间 本资源内含2个工程文件&am…

![编码器、译码器、数据选择器的实现 (VHDL语言) [数字逻辑与数字系统实验一]](https://img-blog.csdnimg.cn/da509f6f67f647b7902090324cc57597.png)